杏彩体育app下载:晶振原理和电容选取的计算

发布时间:2024-05-03 07:08 来源:杏彩体育app 作者:杏彩体育app手机版

,信号质量好,比较稳定,而且连接方式相对简单,不需要复杂的配置电路。因为外围电路固定,相对于无源晶体,有源晶振的缺陷是需要选择好合适输出电平,灵活性较差,而且价格高。

从内部结构看,有源晶振内部构造包含了无源晶振,并且把外围电路封装进去,所以如果能理解无源晶振,也就能理解有源晶振,本篇主要讲解无源晶振。

晶振是利用石英晶体(Quartz-Crystal)的压电效应制成的一种谐振器件。石英本质是矿物质硅石的一种,化学成分是Sio2,从一块晶体上按一定的方位角切割成的薄片称为晶片。

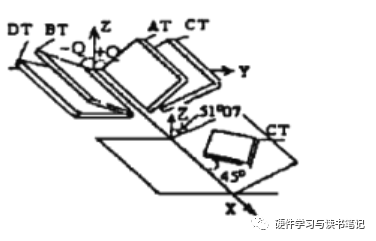

形状是呈角锥形的六棱结晶体,具有各向异性的物理特性。按其自然形状有三个对称轴,电轴X,机械轴Y,光轴Z。

石英谐振器中的各种晶片,就是按照各轴不同角度,切割成正方形、 长方形、 圆形、 或棒型的薄片,如图

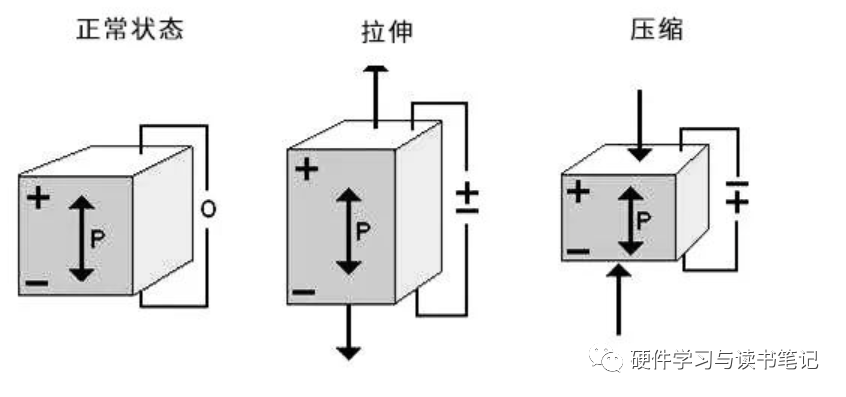

正压电效应:当沿晶体的电轴或机械轴施以张力或压力时, 就在垂直于电轴的两面上产生正、 负电荷, 呈现出电压。

负压电效应:当在垂直于电轴的两面上加交变电压时, 晶体将会沿电轴或机械轴产生弹性变形( 伸张或压缩) , 称为机械振动。

当晶体几何尺寸和结构一定时, 它本身有一固定的机械振动频率。当外加电信号频率在此自然频率附近时, 就会发生谐振现象。它既表现为晶片的机械共振, 又在电路上表现出电谐振。这时有很大的电流流过晶体, 产生电能和机械能的转换。

石英晶体温度系数小和低噪声,石英晶体振荡器的频率稳定度可达到10 -5数量级以上, 具有很高的品质因数, 产生几十kHz几百MHz的振荡频率。

晶振是利用石英晶体的压电效应制成的一种谐振器件,它的基本构成大致是:从一块石英晶体上按一定方位角切下薄片,在它的两个对应面上涂敷银层作为电极,在每个电极上各焊一根引线接到管脚上,再加上封装外壳就构成了晶振。

根据正反压电效应,如果在晶片的两极上加交变电压,晶片就会产生机械振动,同时晶片的机械振动又会产生交变电场。是一种可将电能和机械能相互转化的压电器件,能量转变发生在共振频率点上。

在一般情况下,晶片机械振动的振幅和交变电场的振幅非常微小,但当外加交变电压的频率为某一特定值时,振幅明显加大,比其他频率下的振幅大得多,这种现象称为压电谐振,它与LC回路的谐振现象十分相似。它的谐振频率与晶片的切割方式、几何形状、尺寸等有关。

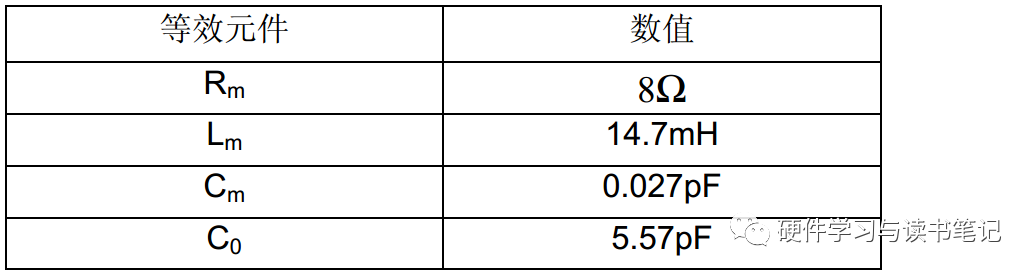

当晶体不振动时, 可以看成是一个平板电容器Co, 称为静电电容。Co与晶片的几何尺寸和电极面积有关。当晶体振荡时,机械振动的惯性可用电感L来等效。

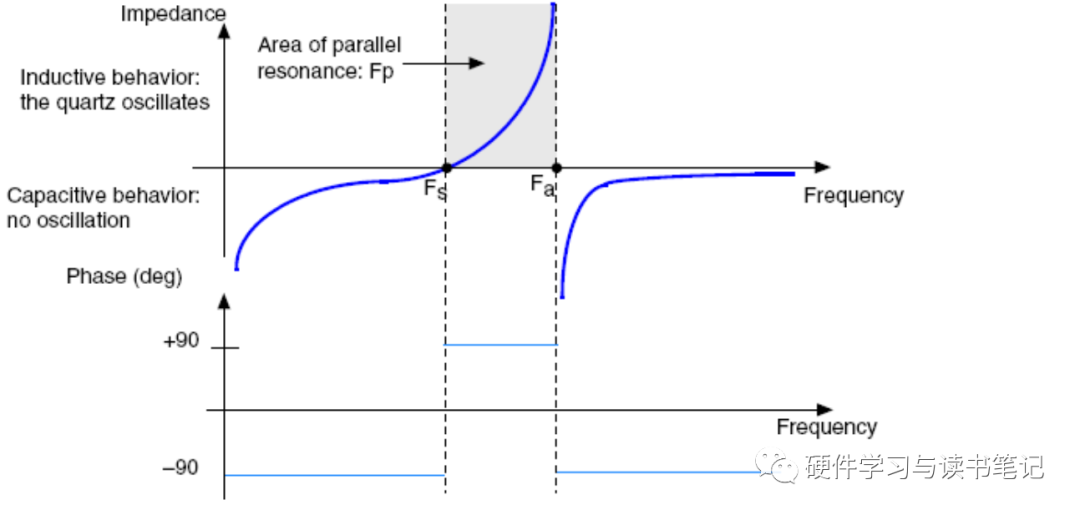

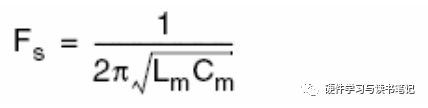

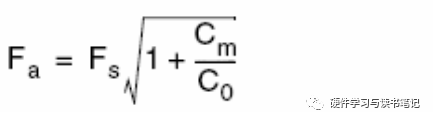

其中Fs的是当电抗Z=0时的串联谐频率(它是Lm、Cm和Rm支路的谐振频率),其表达式如下:

在Fs到Fa的区域即通常所谓的联谐振状态(该区域就是晶振的正常工作区域,Fa-Fs就是晶振的带宽。)

带宽越窄,品质因素越高,振荡频率越稳定, 在此区域晶振呈电感特性,从而带来了相当于180 °的相移。

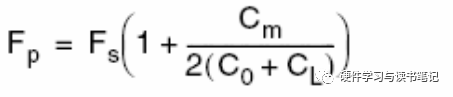

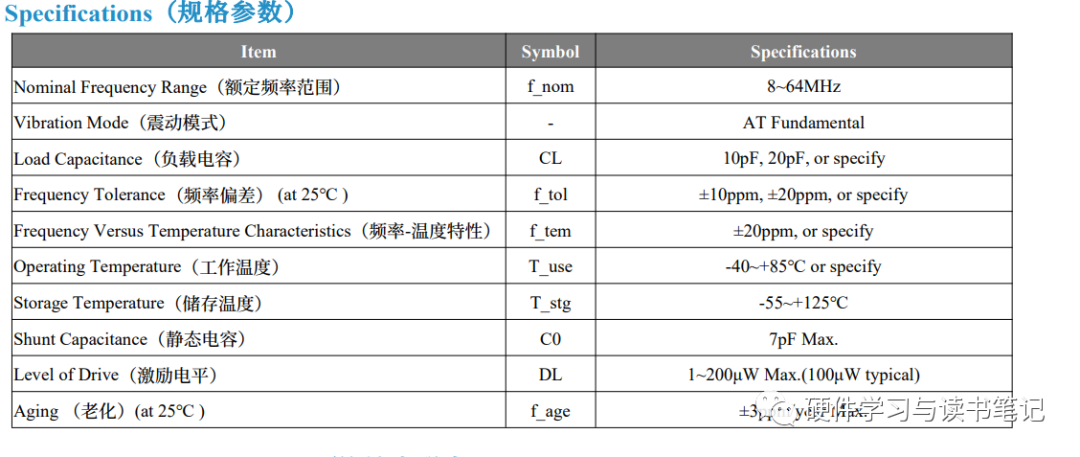

制造商在其产品说明书中会指定外部负载电容CL值的原因。通过指定外部负载电容CL值,可以使晶体振荡时达到其标称频率。

如果该晶振的CL为10pF,则其振荡频率为:FP = 7995695Hz。要使其达到准确的标称振荡频率8MHz,CL应该为4.02pF。

晶振频率是工作频率的简称,晶振元件在电路中正常工作时候的理想频率就是工作频率,这个参数在晶振设计好的时候就固定好了,我们在采购的时候应该顺应需求选择合理选择。

由时间引起的频率偏移,这个指标对于精密仪器是必要的。它没有明确的测试条件,而是由制造商通过对所有产品的计划采样持续监督。某些晶体元素可能比规定的老化率有些偏差,这是允许的,老化问题的最佳解决方案只能靠制造商和用户之间的密切协商。

用晶体元件测定负载共振频率FL的有效外电容,晶体元件规范中的cl是一个测试条件和一个使用条件,可根据用户的具体用途调整,以微调实际工作频率(即制造公差可调整)。然而它具有一个合适的值,否则它会使振荡电路老化。其值通常是10PF、15PF、20PF、30PF、50PF等,其中Cl用于串联谐振电路,其操作频率为晶体的谐振频率。对于某些晶体(包括非封装振荡器的应用),0.5pf的实际电容的误差可能导致给定负载电容器(特别是小负载电容器)下的频率误差为+-6,因此负载电容是订单规范的一个重要指标。

前文我们有计算过晶振的负载电容,一般规格书中有推荐的负载电容值,它是指晶振要正常振荡时所需的电容。

很多工程师误解以为这个晶振的CL参数就是等同于晶振振荡电路里的C1 C2两个外挂电容的串联等效电容C1*C2/(C1+C2)。其实负载电容是指晶振的两条引线连接IC 块内部及外部所有有效电容之和.

式中C1,C2为分别接在晶振的两个脚上和对地的电容,Cic集成电路内部电容+△CPCB上电容,经验值为3至5pf。

假设一个10PF的负载电容的晶振电路,外挂旁路电容的大小应该可以这样推算:1)假设杂散电容为5pF,C1/C2=(10-5)*2 =10PF;

2)假设按照3PF来推算,C1/C2=(10-3)*2=14PF,可以就近选择15PF接入电路。如果不做精确的回路调查工作,可以依照此数字做大概的推算并调试。

1、位置要选对:晶振内部是石英晶体,如果不慎掉落或受不明撞击,石英晶体易断裂破损,所以晶振的放置远离板边,靠近MCU的位置布局。

2、两靠近:耦合电容应尽量靠近晶振的电源管脚,如果多个耦合电容,按照电源流入方向,依次容值从大到小摆放;晶振则要尽量的靠近MCU。

3、走线短:在电路系统中,高速时钟信号线优先级最高,一般在布线时,需要优先考虑系统的主时钟信号线。时钟线是敏感信号,频率越高,要求走线尽量的短,保证信号的失线、高独立:尽可能保证晶振周围的没有其他元件。防止器件之间的互相干扰,影响时钟和其他信号的质量。网传是300mil内不要布线,实际在设计中并没有如此严格。

6、谨慎选择C1、C2的容值。尽量按照晶振厂家提供的推荐值设计。在满足起震要求的前提下,C1、C2的取值可以尽量小,能缩短石英晶振起震时间。